# International Journal of Advance Engineering and Research Development

e-ISSN (O): 2348-4470

p-ISSN (P): 2348-6406

Volume 5, Issue 04, April -2018

## DEVISE OF MULTIBIT FLIP FLOP INTEGRATION WITH CLOCK DATING METHOD

\*ENDARAPU THIRUPATHI, \*\* MD.MISBAHUDDIN,

- \* (Academic Assistant, Department of ECE, JNTUH College of Engineering Manthani, INDIA

- \*\* (Assistant Professor, Department of ECE, JNTUH College of Engineering Manthani, INDIA)

ABSTRACT:Power reduction plays an essential position in VLSI layout. The Data-pushed clock gating is used to reducing strength consumption in synchronous circuits. Common clock gating is used for energy saving. However, clock gating nevertheless leaves large quantity of redundant clock pulses. Multi-bit turn-flop is likewise used to reduce electricity intake. Clock gating is a popular method used in many synchronous circuits for lowering dynamic power dissipation. Gating manually inserted into the register transfer level layout. When a common sense unit is a clock, its underlying sequential factors acquire the clock signal regardless of whether or not or no longer will they toggle within the next cycle. In this turn-flops are grouped so they share a commonplace clock permitting signal to lessen the hardware overhead. Since Flip-Flops are the important building blocks of the Digital design which may additionally depend on the Clock signal. So those Flip-Flops eat greater strength than another circuit. In order to lessen the dynamic losses of the flip-flop right here we introduce a records-driven clock gating approach and later we proposed to look beforehand Clock Gating method with Auto-Gated Flip-Flop.

Keywords: SOC, LFSR (Linear feedback shift register), test data, chips, flip flop.

#### 1. INTRODUCTION:

There are many strategies used to lessen the dynamic energy are advanced, in which clock gating is predominant. Ordinarily, whilst a logic unit is clocked, it's far based at the sequential factors receiving the clock signal; sequentially they'll toggle in the next cycle whether or not its miles required or not. With clock gating, the clock signals are AND with explicitly predefined enabling alerts. Clock gating is employed in any respect tiers: system architecture, block design, logic layout, and gates. Clock gating is a popular method used in lots of synchronous circuits for decreasing dynamic electricity dissipation. Clock gating saves electricity by means of adding extra logic to a circuit to prune the clock tree. Pruning the clock disables portions of the circuitry in order that the flip-flops in them do not have to switch states. Switching states consumes strength. When now not being switched, the switching energy intake is going to 0, and only leakage currents are incurred. Clock allowing indicators are normally introduced by using designers throughout the machine and clock layout levels, wherein the inter-dependencies of the diverse functions are well understood. In comparison, it is very difficult to define such signals in the gate level, especially in control logic, since the inter-dependencies some of the states of numerous turn-flops depend on robotically synthesized common sense. A version for records-pushed gating is advanced based on the toggling hobby of the constituent FFs. The most beneficial fan-out of a clock gate yielding maximal power financial savings is derived based at the common toggling information of the person FFs, technique technology, and cell library in use. In trendy, the country transitions of FFs in virtual structures depend on the records them manner. Assessing the effectiveness of records-driven clock gating calls for, consequently, sizable simulations and statistical evaluation of the FFs' activity. Another grouping of FFs for clock switching electricity discount, referred to as multi bit FF. Clock gating works by way of taking the enable conditions connected to registers and makes use of them to gate the clocks. Therefore it's far imperative that a design have to incorporate these permit conditions as a way to use and gain from clock gating. This clock gating system can also shop significant die region as well as electricity since it eliminates massive numbers of mixes and replaces them with clock gating good judgment. This clock gating good judgment is generally in the shape of "Integrated clock gating" (ICG) cells. However, note that the clock gating common sense will alternate the clock tree shape because the clock gating logic will sit down within the clock tree. In evaluation, it's far very difficult to outline such alerts at the gate stage, especially on top of things logic, for the reason that inter-dependencies a few of the states of various turn-flops rely on automatically synthesized good judgment. There is a massive gap among block disabling this is pushed from the HDL definitions, and what can be carried out with statistics know-how regarding the flip-flops sports and the way they're correlated with each different.

#### 2. RELATED STUDY:

The statistics-pushed elements also are subjected to clock gating to keep away from redundancy in terms of dynamic strength dissipation. The switching of facts both from zero-1 or 1-zero states is taking because the constraint for applying the gating. Whenever there no incidence of latest records the clock is gated to the turn flop and the equal is taking place to a group of such turn-flops. A massive quantity of flip-flops driven through identical clock sign is subjected to clock gating through the use of grouping. Unfortunately, this couldn't be completed to large amount, because it depends at the physical proximity of turn flops. This may be powerful for two or three in quantity, which is likewise called sharing of inverters. The inverter using the slave latch is shared with latches of different turn flops. In the current years grouping is performed based mostly on toggling similarity and on the same time bodily proximity which includes a prolonged style of turn flops. The outputs obtained from this organization can be similarly processed via combinational circuits. Digital circuits usually have a few inputs and generate digital outputs for this reason. Some digital circuits are not clocked, that means that the enter applied to the circuit flows through virtual gates with none timing or storage and generates the output. It best takes a time same to the propagation do away with time to reap the output. MBFF attempts to physical merge FFs right into an unmarried cell such that the inverters using the clock pulse into its grasp and slave latches are shared amongst all FFs in a hard and fast. MBFF grouping is specifically pushed with the aid of way of the physical role proximity of individual FFs, even as grouping for information-pushed clock gating ought to combine toggling similarity with physical role issues. Also, noise margins are reduced, developing the danger of chip failure because of crosstalk. CMOS virtual circuits arise in paperwork: dynamic and static. Dynamic energy dissipation occurs inside the not unusual sense gates which may be in the technique of switching from one kingdom to some other. During this gadget, any internal and outside capacitance associated with the gate's transistors must be charged, thereby consuming strength. Static power dissipation is associated with inactive right judgment gates.

#### 3. METHODOLOGY:

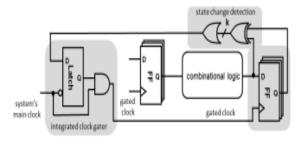

Power discount is carried out by the use of clock gating. With clock gating, the Clock indicators are multiply with an AND gate common sense to explicitly predefined allowing sign. But this clock gating still leaves a big quantity of redundant clock pulses. Although considerably growing layout productivity, such gear require the employment of a long chain of automatic synthesis algorithms, from register switch stage (RTL) all the way down to gate degree and net list. Unfortunately, such automation leads to a big quantity of needless clock toggles, as a result growing the quantity of wasted clock pulses at turn flops (FFs) as proven on this paper via several business examples. Consequently, improvement of computerized and effective strategies to lessen this inefficiency is applicable. In the sequel, we can use the phrases toggling, switching, and hobby interchangeably. Multi-bit Flip-Flop technique is to eliminate the whole inverter variety by way of sharing the inverters in the turn-flops. Data-driven clock gating reduces redundant clock pulses. Combination of Multi-bit Flip-Flop with Data-pushed clock gating will increase the in addition power saving. Xilinx software program device is used for imposing this proposed system. This paper research records-pushed clock gating, employed for FFs at the gate level, that's the maximum aggressive feasible. The clock signals using an FF is disabled (gated) while the FFs nation is not subject to alternate within the subsequent clock cycle. Data-driven gating is inflicting area and energy overheads that need to be considered. In a try to lessen the overhead, its miles proposed to organization numerous FFs to be driven via the equal clock signal, generated through bringing the allowing signals of the individual FFs. This may, however, decrease the disabling effectiveness. It is consequently beneficial to group FFs whose switching sports are tremendously correlated and derive a joint allowing sign. Those are later being automatically synthesized into clock allowing alerts on the gate degree. In many instances, clock allowing signals are manually added for every FF as a part of a design methodology. Still, while modules at a high and gate stage are clocked, the country transitions in their underlying FFs rely on the facts being processed. It is important to observe that the entire dynamic power ate up by using a machine stems from the intervals in which modules' clock signals are enabled. Therefore, no matter how surprisingly small, this era is, assessing the effectiveness of clock gating requires enormous simulations and statistical analysis of FFs toggling activity, as offered eventually.

Fig.3.1. Model diagram.

#### 4. SIMULATION RESULTS:

Finding sets of FFs that decrease the wide type of redundant clock pulses is not enough to maximize energy financial savings. Grouping ought to account for the on-die places of FFs and gaiters, which have an effect at the strength intake due to the capacitive masses attributable to their connections. The bodily places of FFs affect also the postpone and clock skew, and it's far consequently applicable for FFs driven on the same time thru the same clock gaiter, to be located in proximity to each different.

Fig.4.1. Simulated diagram.

And power consumptions calculated. Re-walking the take a look at bench of Step 1 to affirm the whole identification of FFs' outputs earlier than and after the creation of gating logic. Although records-driven gating, by way of its very definition, need to no longer exchange the good judgment of signals, and hence FFs toggling ought to stay identical, a strong design waft must put into effect this step.

#### 5. CONCLUSION:

Clock gating is utilized in FIFO to reduce the electricity consumption. For further electricity saving data-driven clock gating and multi bit turn-flops are used in sequential circuits. Common clock gating is used for electricity saving. But clock gating still leaves a bigger quantity of redundant clock pulses. Multi bit flip-flop is also used to lessen power consumption. Using of Multi bit Flip-Flop method is to get rid of the full inverter number by sharing the inverters inside the flip-flops. Combination of Multi-bit Flip-Flop with Data-driven clock gating will increase the further power saving. Xilinx software tool is used for imposing this proposed device. The mixture of facts-driven gating with MBFF in a try to yield further energy financial savings.

#### **REFERENCES:**

- [1] V. G. Oklobdzija, Digital System Clocking—High Performance and Low-Power Aspects. New York, NY, USA: Wiley, 2003.

- [2] L. Benini, A. Bogliolo, and G. De Micheli, "A survey on design techniques for machine-stage dynamic electricity management Syst., vol. Eight, no. 3, pp. 299–316,Jun. 2000.

- [3] R.Saranya, K.Radhika, Dr.S.Nirmala, K.Priyameenkshi, "strength optimization the use of clock gating techniques," international journal of modern studies in computer and communication enginnering[IJIRCCE], vol 2,difficulty eleven, Nov 2014.

- [4] C. Chunhong, K. Changjun, and S. Majid, "Activity-touchy clock tree creation for low electricity," in Proc. Int. Symp. Low Power Electron. Design, 2002, pp. 279–282.

- [5] A. Farrahi, C. Chen, A. Srivastava, G. Tellez, and M. Sarrafzadeh, "Activity-pushed clock layout," IEEE Trans. Comput.-Aided Design Integr. Circuits Syst., vol. 20, no. 6, pp. 705–714, Jun. 2001.

### International Journal of Advance Engineering and Research Development (IJAERD) Volume 5, Issue 04, April-2018, e-ISSN: 2348 - 4470, print-ISSN: 2348-6406

- [6] W. Shen, Y. Cai, X. Hong, and J. Hu, "Activity and sign up placement aware gated clock network design," in Proc. Int. Symp. Phys. Design, 2008, pp. 182–189. 778 IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION (VLSI) SYSTEMS, VOL. 22, NO. Four, APRIL 2014

- [7] M. Donno, E. Macii, and L. Mazzoni, "Power-conscious clock tree making plans," in Proc. Int. Symp. Phys. Design, 2004, pp. 138–147.

- [8] Dr. S. Nirmala and R. Praveena, "Modified Partial Product Bypassing Multiplier for DSP Application," International Conference on Innovation in Electronics and Communication Engineering (ICIECE), pp. 128, Aug 2013.

- [9] S. Wimer and I. Koren, "The Optimal fan-out of clock community for power minimization via adaptive gating," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 20, no. 10, pp. 1772–1780, Oct. 2012.