Scientific Journal of Impact Factor (SJIF): 4.72

e-ISSN (O): 2348-4470 p-ISSN (P): 2348-6406

# International Journal of Advance Engineering and Research Development

Volume 4, Issue 12, December -2017

# UTILIZATION OF APB INTERFACE IN LIGHT OF AMBA 4.0

M.Poojitha<sup>1</sup> Tejender Singh <sup>2</sup> P.Prassana Kumari <sup>3</sup>

1M.Tech Student, Dept of ECE, DVR College Of Engineering and Technology, Kashipur, Sangareddy, Medak, Telangana, India

2Assistant Professor, of ECE, DVR College Of Engineering and Technology, Kashipur, Sangareddy, Medak, Telangana, India

3 Associate Professor, of ECE, DVR College Of Engineering and Technology, Kashipur, Sangareddy, Medak, Telangana, India

**ABSTRACT**:- ARM presented the Advanced Microcontroller Bus Design (AMBA) 4.0 determinations, which incorporates advanced extensible Interface (AXI) 4.0. AMBA transport convention has turned into the accepted standard SoC transport. That implies an ever increasing number of existing IPs must have the capacity to speak with AMBA 4.0 transport. In view of AMBA 4.0 transport, we composed an Protected innovation (IP) center of Advanced Peripheral Bus (APB) connect, which interprets the AXI4.0-lite exchanges into APB 4.0 exchanges. The extension gives an interface between the elite AXI transport and low-control APB space.

### 1. Introduction

There are many organizations that create center IP for SoC items. The interfaces to these centers can contrast from organization to organization and can now and then be restrictive in nature. The SoC engineer at that point must consume time, exertion, and cash to make "extension" or "paste" rationale that permits the greater part of the centers inside the SoC to discuss legitimately with each other. Inconsistent interfaces are in this way boundaries to both IP engineers and SoC designers. SoC incorporated circuits imagined b1y this subcommittee traverse a wide broadness of utilizations, target framework expenses, and levels of execution and joining.

Coordinated circuits have entered the time of System-on-a-Chip (SoC), which alludes to incorporating all segments of a PC or other electronic framework into a solitary chip. It might contain advanced, simple, blended flag, and regularly radio-recurrence works all on a solitary chip substrate. With the expanding configuration estimate, IP is an inescapable decision for SoC plan. Also, the far reaching utilization of a wide range of IPs has changed the idea of the outline stream, making On-Chip Busses (OCB) basic to the plan. Of all OCBs existing in the market, the AMBA transport framework is generally utilized as the true standard SoC transport. On March 8, 2010, ARM reported accessibility of the AMBA 4.0 details. As the true standard SoC transport, AMBA transport is broadly utilized as a part of the elite SoC outlines. The AMBA determination characterizes an on-chip correspondence standard for planning elite installed microcontrollers. ARM presented the Advanced Microcontroller Bus Architecture (AMBA) 4.0 particulars in March 2010, which incorporates advanced extensible Interface (AXI) 4.0. AMBA transport convention has turned into the true standard SoC transport. That implies an ever increasing number of existing IPs must have the capacity to speak with AMBA 4.0 transport. In view of AMBA 4.0 transport, This plan is an Intellectual Property (IP) center of AXI (Advanced extensible Interface) Lite to APB (Advanced Peripheral Bus) Bridge, which interprets the AXI4.0-lite exchanges into APB 4.0 exchanges. The scaffold gives interfaces between the superior AXI transport and low-control APB space.

# 2. Literature Survey

The Advanced Microcontroller Bus Architecture (AMBA) is utilized as the on-chip transport in framework on-a-chip (SoC) plans. Since its initiation, the extent of AMBA has gone a long ways past microcontroller gadgets, and is presently broadly utilized on a scope of ASIC and SoC parts incorporating applications processors utilized as a part of current compact cell phones like PDAs.

The AMBA convention is an open standard, on-chip interconnect determination for the association and administration of useful pieces in a System-on-Chip (SoC). It encourages right-first-time advancement of multi-processor outlines with vast quantities of controllers and peripherals.

# 2.1 System on Chip (SoC)

SOC is a gadget which coordinates all the PC gadgets on to one chip, which keeps running with desktop working frameworks like windows, Linux and so forth. They appear differently in relation to a microcontroller is one of degree. Microcontrollers ordinarily have under 100 KB of RAM (regularly only a couple of kilobytes) and frequently truly are single-chip-

frameworks, while the term SoC is commonly utilized with all the more effective processors, equipped for running programming, for example, the desktop variants of Windows and Linux, which require outer memory chips (streak, RAM) to be helpful, and which are utilized with different outside peripherals. To put it plainly, for bigger frameworks framework on a chip is metaphor, demonstrating specialized heading more than reality: expanding chip reconciliation to diminish producing costs and to empower littler frameworks. Many intriguing frameworks are excessively intricate, making it impossible to fit on only one chip worked with a procedure improved for only one of the framework's assignments. When it isn't plausible to build a SoC for a specific application, an option is a framework in bundle (SiP) containing various chips in a solitary bundle. In extensive volumes, Sock is accepted to be more savvy than SiP since it expands the yield of the manufacture and in light of the fact that its bundling is basic

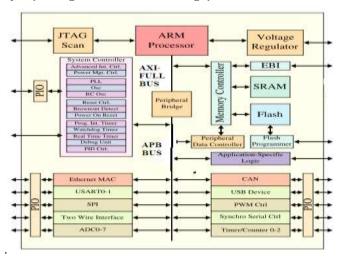

### 2.1.1 Structure of Sock

A run of the mill Sock comprises of:

- A microcontroller, chip or DSP core(s). Some Sock called multiprocessor framework on chip (MPSoC)—incorporate more than one processor center.

- Memory pieces including a choice of ROM, RAM, EEPROM and glimmer memory.

- Timing sources including oscillators and stage bolted circles.

- Peripherals including counter-clocks, constant clocks and power-on reset generators.

- Analog interfaces including ADCs and DACs.

- Voltage controllers and power administration circuits.

These squares are associated by either a restrictive or industry standard transport, for example, the AMBA transport from ARM Holdings. DMA controllers course information specifically between outer interfaces and memory, bypassing the processor center and consequently expanding the information throughput of the Sock

Fig. 2.1 ARM-Sock Block Diagram

# 2.2 Advanced Microcontroller Bus Architecture (AMBA)

A run of the mill Sock comprises of:

- A microcontroller, chip or DSP core(s). Some Sock called multiprocessor framework on chip (MPSoC)—incorporate more than one processor center.

- Memory pieces including a choice of ROM, RAM, EEPROM and glimmer memory.

- Timing sources including oscillators and stage bolted circles.

- Peripherals including counter-clocks, constant clocks and power-on reset generators.

- Analog interfaces including ADCs and DACs.

- Voltage controllers and power administration circuits.

These squares are associated by either a restrictive or industry standard transport, for example, the AMBA transport from ARM Holdings. DMA controllers course information specifically between outer interfaces and memory, bypassing the processor center and consequently expanding the information throughput of the Sock .

# 2.2.1 AMBA Specifications

Ip re-utilize is a basic part in decreasing soc advancement costs and timescales. amba determinations give the interface standard that empowers ip re-utilize meeting the basic prerequisites of:

# 2.2.2 Design principles of AMBA

The essential part of a Sock isn't just which segments or squares it houses, yet in addition how they are interconnected. AMBA is an answer for the pieces to interface with each other. The target of the AMBA is to:

- Facilitate right-first-time improvement of inserted microcontroller items with at least one CPUs, GPUs or flag processors.

- Be innovation free, to permit reuse of IP centers, fringe and framework microcells crosswise over differing IC forms.

- Encourage particular framework configuration to enhance processor autonomy, and the advancement of reusable fringe and framework IP libraries.

- Minimize silicon foundation while supporting superior and low power on-chip correspondence.

# 2.2.3 AMBA 4.0 specification buses/interfaces

- 1. Advanced Extensible Interface (AXI)

- a. AXI4

- b. AXI4-Lite

- c. AXI-4 Stream

- 2. Advanced High-execution Bus (AHB)

- 3. Advanced System Bus (ASB)

- 4. Advanced Peripheral Bus (APB)

- 5. Advanced Trace Bus (ATB)

In this venture these are to be utilized Advanced eXtensible Interface (AXI4) and Advanced Peripheral Bus (APB) in light of the fact that these are high transmission capacity information exchange between superior gadgets like processor, DMA, RAM etc..., Furthermore, Peripheral gadgets.

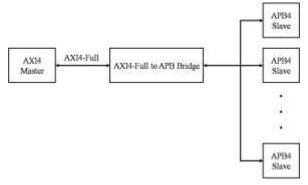

# 2.2.4 AXI4 to APB Bridge

In this examination, we concentrated for the most part on the execution part of an AXI4 to APB Bridge. The AXI4 to APB Bridge gives an interface between the superior AXI area and the low power APB space. It shows up as a slave on AXI transport however as an ace on APB that can access up to sixteen slave peripherals. Read and compose exchanges on the AXI transport are changed over into comparing exchanges on the APB. The AXI4 to APB connect Block chart is appeared in Figure.(2.4)

Fig. 2.4 AXI to APB Bridge Block Diagram

# 2.2.5 Features of bridge

The Xilinx AXI to APB Bridge is a delicate IP center with these highlights:

- AXI interface depends on the AXI4 particular.

- APB interface depends on the APB3 particular, underpins discretionary APB4 choice.

- Supports 1:1 (AXI:APB) synchronous clock proportion.

- Connects as a 32-bit slave on 32-bit AXI4.

- Connects as a 32-bit ace on 32-bit APB3/APB4.

# 3. Proposed model

Coordinated circuits have entered the period of System-on-a-Chip (Sock), which alludes to incorporating all segments of a PC or other electronic framework into a solitary chip. It might contain computerized, simple, blended flag, and regularly radio-recurrence capacities – all on a solitary chip substrate. With the expanding configuration estimate, IP is an unavoidable

# International Journal of Advance Engineering and Research Development (IJAERD) Volume 4, Issue 12, December-2017, e-ISSN: 2348 - 4470, print-ISSN: 2348-6406

decision for Sock plan. Also, the across the board utilization of a wide range of IPs has changed the idea of the plan stream, making On-Chip Busses (OCB) basic to the outline.

The three primary criteria used to choose transports for thought were:

- The level of acknowledgment and infiltration in the business: It would ruin acknowledgment of the transport pecking order if a dark arrangement of transports were picked that did not have a current industry bolster structure and library of valuable accessible IP.

- The specialized capacity to help the extensive variety of utilizations found in average SoCs: It would be an oversight to determine an arrangement of transports that did not have the highlights or adequate data transmission to help basic Sock applications.

- The simplicity of interfacing to Power Architecture processors: Given that the fundamental objective of Power.org is to advance Power Architecture processors, it would look bad for the Power.org Bus

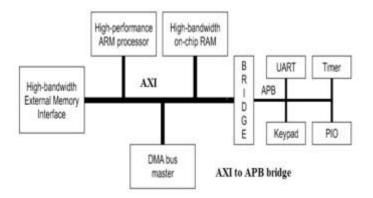

### 3.1 Overview

An AMBA-based microcontroller commonly comprises of an elite framework spine transport (AMBA AXI), ready to maintain the outer memory data transmission, on which the CPU, on-chip memory and other Direct Memory Access (DMA) gadgets live. This transport gives a high-data transmission interface between the components that are engaged with the larger part of exchanges. Likewise situated on the elite transport is a scaffold to the lower transmission capacity APB, where the greater parts of the fringe gadgets in the framework are found.

Fig. 3.1 Overview of AXI to APB Bridge

# 3.3 Features of the project

We give a usage of AXI4-Lite to APB Bridge which has the accompanying highlights:

- 32-bit AXI slave and APB ace interfaces.

- PCLK clock space totally autonomous of ACLK clock area.

- Support up to 16 APB peripherals.

- Support the PREADY flag which means hold up states on AXI.

- An blunder on any move brings about SLVERR as the AXI read/compose reaction.

### 4. Advanced Extensible Interface (AXI) Protocol

The AMBA AXI convention is focused at elite, high-recurrence framework plans and incorporates various highlights that make it reasonable for a fast submicron interconnects.

# 4.1 The AXI protocol:

- Is appropriate for high-transmission capacity and low-idleness outlines

- Provides high-recurrence operation without utilizing complex extensions

- Meets the interface necessities of an extensive variety of segments

- Is appropriate for memory controllers with high introductory access idleness

- Provides adaptability in the usage of interconnect models is in reverse perfect with existing AHB and APB interfaces.

### 5.Advanced Peripheral Bus (APB) Protocol

The Advanced Peripheral Bus (APB) is a piece of the Advanced Microcontroller Bus Architecture (AMBA) convention family. It characterizes an ease interface that is streamlined for insignificant power utilization and decreased interface multifaceted nature.

# International Journal of Advance Engineering and Research Development (IJAERD) Volume 4, Issue 12, December-2017, e-ISSN: 2348 - 4470, print-ISSN: 2348-6406

Every flag progress are just identified with the rising edge of the clock to empower the combination of APB peripherals effortlessly into any outline stream. Each exchange takes no less than two cycles.

The APB would interface be able to with the AMBA Advanced High-execution Bus Lite (AHB-Lite) and AMBA Advanced Extensible Interface (AXI).

The APB Bus is the most reduced execution transport in the AMBA family. There are separate address (PADDR), compose information (PWDATA), and read information (PRDATA) transports, up to 32-bits each. With 7 extra control signals, there can be up to 103 I/O for each APB slave. There is one APB ace, more often than not the scaffold from a higher execution transport that starts an exchange by stating the fitting PSELn motion with PADDR. PWRITE is dynamic for a compose and inert on a read. PENABLE is attested in the second clock, and is held dynamic until the point that PREADY is returned by the slave. The base exchange, read or compose, is two tickers. APB slaves additionally have the choice of embeddings sit tight states for peruses or composes by withholding PREADY. There is a discretionary PSLVERR flag utilized by the slave to report a mistake on a read or compose with PREADY.

Expecting a recurrence of 133MHz, (which ought to be achievable in a 90nm or littler process) and the most extreme information transport widths of 32-bits, the general APB data transmission could be as high as 267MB/s, yet that accept that none of the APB slaves would embed any hold up states. Additionally, the aggregate APB data transfer capacity must be shared between the greater part of the APB slaves.

### 5.1 With wait states

Figure 5.3 shows how the PREADY flag can broaden the exchange. The exchange is broadened if PREADY is driven LOW amid an Access stage. The convention guarantees that the accompanying stay unaltered for the extra cycles:

- · address, PADDR

- · write flag, PWRITE

- select flag, PSEL

- enable flag, PENABLE.

Figure 5.3 demonstrates that two cycles are included utilizing the PREADY flag. Be that as it may, you can include any number of extra cycles, from zero upwards.

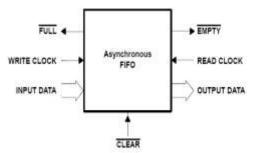

# 6. Asynchronous FIFO

A nonconcurrent FIFO alludes to a FIFO outline where information esteems are composed to a FIFO cradle from one clock space and the information esteems are perused from a similar FIFO cushion from another clock area, where the two clock areas are offbeat to each other. Offbeat FIFOs are utilized to securely pass information starting with one clock area then onto the next clock space.

There are numerous approaches to do offbeat FIFO configuration, including many wrong ways. Most inaccurately actualized FIFO outlines still capacity appropriately 90% of the time. Most practically adjust FIFO outlines work appropriately 99%+ of the time. Sadly, FIFOs that work appropriately 99%+ of the time have configuration defects that are normally the most Difficult to recognize and investigate (in the event that you are sufficiently fortunate to see the bug before transportation the item), or the most exorbitant to analyze and review.

# 6.1 Connections of an Asynchronous FIFO

The Asynchronous FIFO is a First-In-First-Out memory line with control rationale that performs administration of the read and compose pointers, age of status banners, and discretionary handshake signals for interfacing with the client rationale.

Full Flag: Generates an Almost Full flag, demonstrating that one extra compose can be performed before the FIFO is full. Practically Empty Flag: Generates an Almost Empty flag, demonstrating that one extra read can be performed before the FIFO is void. The discretionary handshaking control signals (recognize as well as mistake) can be empowered by means of the Handshaking Options catch. Whenever chose, a popup exchange box will show up.

Read Acknowledge Flag: Asserted dynamic on the clock cycle after an effective read has happened. This flag, when chosen, can be made dynamic high or low through the GUI.

Read Error Flag: Asserted dynamic on the clock cycle after a read from the FIFO was endeavored, however not fruitful. This flag, when chosen, can be made dynamic high or low through the GUI. Compose Acknowledge Flag: Asserted dynamic on the clock cycle after a fruitful compose has happened. This flag, when chosen, can be made dynamic high or low through the GUI

Compose Error Flag: Asserted dynamic on the clock cycle after a keep in touch with the FIFO was endeavored, however not effective. This flag, when chosen, can be made dynamic high or low through the GUI.

7. Simulation And Synthesis Results

### 7.1 Introduction

This section clarifies the Simulation and Synthesis consequences of usage of interfacing between elite drivers to low power gadgets utilizing APB connect.

### 7.2 Simulation Results

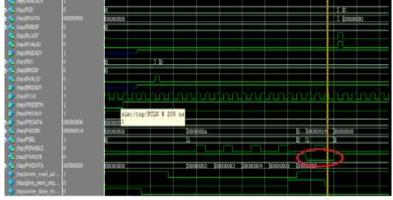

Reproduction is to check your outline. Consequently it is initial step after your plan and coding is finished. It is absolutely programming action where you check your plan utilizing test systems like ModelSim. Figure 8.1 and Figure 8.2 shows reproduction aftereffect of five distinct diverts in AXI convention and diverse flags in APB convention. Here both AXI and APB worked on various clock spaces these tickers are spoken to as ACLK and PCLK separately in following two figures.

The five unique directs in AXI are appeared in figure 8.1. These signs are clarified in chapter4.

Figure 8.1 Different channels in AXI.

Figure 8.2 APB signals

Figure 8.2 demonstrates the diverse flags in APB space. These signs are clarified in chpter5. Both ACLK and PCLK are certain edge timekeepers. These are two worldwide clock flags all signs are tested at rising edge of the clock.

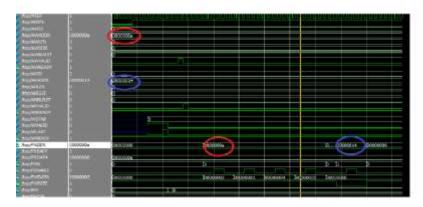

Figure 8.3 Address mapping between AXI and APB

Figure 8.3 demonstrates the compose address (AWADDR) and read address (ARADDR) in the AXI are changed over into PADDR in APB side. This mapping is finished by APB connect. In the figure it demonstrates that AWADDR = 0000000a = PADDR i.e ace composes the information in the 0000000a address area. This compose address mapping is appeared in the figure 8.3 by red air pocket.

So also ARADDR = 00000014 = PADDR i.e ace (AXI) peruses the date from the area 00000014 which is in slave (APB) side. This mapping is appeared in figure 8.3 by utilizing blue air pocket.

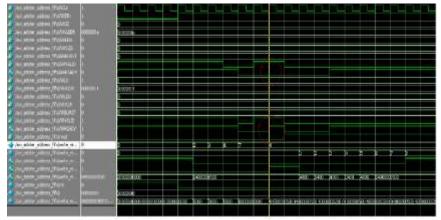

Figure 8.4 Data transfer between AXI and APB

Figure 8.4 demonstrates the compose and read information exchange amongst AXI and APB i.e exchange amongst ace and slave. Here ace put the four information things 00000002,00000003,00000004,00000005. What's more, it give the main deliver area to slave where slave should store the information things. That address area is 0000000a. So here slave take the four information things and store them in the 0000000a address area. In the figure 8.4 this operation appears by utilizing red air pocket. Essentially read information from slave to the ace. Here ace read the information 00000006 from the slave from the address area of 00000014. In the figure it can appeared by utilizing yellow air pocket.

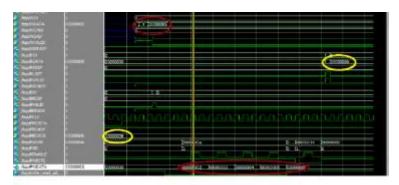

Figure 8.5 Operation of PWRITE signal in APB

Figure 8.5 shows how PWRITE flag controls the read and compose operation in the APB. On the off chance that this flag is HIGH APB performs compose operation and when it is LOW APB performs read operation.

Figure 8.6 AXI arbitration

Figure 8.6 demonstrates the assertion amongst read and compose demands. Whenever read and compose demands are happen at the same time APB connect gives the greater need to peruse ask. It appears in the figure 8.6 here when fifo has just a single discharge area and read and compose demands are happen around then APB connect takes read ask for by put the AWREADY flag LOW and ARREADY flag HIGH.

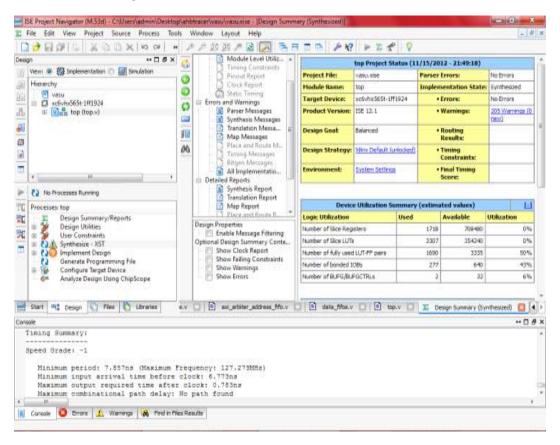

# 7.3 Synthesis Results

Combination is the way toward building a door level netlist from an enroll exchange level model of a circuit portrayed in Verilog HDL. A blend framework is a middle of the road step, producing a netlist that is contained enroll exchange level squares, for example, flip-flops, math rationale units, and multiplexers interconnected by wires.

# 7.4 Synthesis results of APB bridge

Figure 8.7 Synthesis report of APB bridge

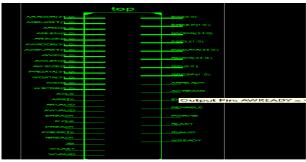

# 7.5 RTL Schematic of APB bridge

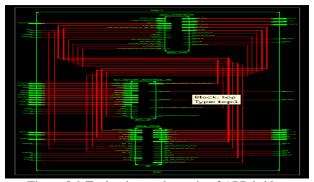

RTL View is a Register Transfer Level graphical portrayal of outline. Figure 8.8 demonstrates the RTL schematic of APB connect.

Figure 8.8 RTL schematic of APB bridge

# 7.6 Technology schematic of APB bridge

Innovation see is graphical portrayal of configuration, Figure 8.9 demonstrates the innovation perspective of the yield organize plan of APB connect.

Figure 8.9 Technology schematic of APB bridge

# 7.7 Device utilization summary of APB bridge

| Logic Utilization | Used | Available | Area<br>Utilization |

|-------------------|------|-----------|---------------------|

| Number of         | 1713 | 708480    | 0%                  |

| registers         |      |           |                     |

| Number of slice   | 3307 | 354240    | 0%                  |

| LUTs              |      |           |                     |

| Number of         | 1690 | 3335      | 50%                 |

| LUTFF pairs       |      |           |                     |

| Number of bonded  | 277  | 640       | 43%                 |

| IOBs              |      |           |                     |

| Number of         | 2    | 32        | 6%                  |

| GCLKs             |      |           |                     |

Table 8.1 Design utilization summary

# 7.8 Timing Summary

Speed Grade: -1

Minimum period: 7.161ns (Maximum Frequency: 139.643MHz)

Minimum input arrival time before clock: 6.885ns Maximum output required time after clock: 0.777ns Maximum combinational path delay: No path found

### 8. Conclusions

The APB connects give an execution of AXI4-Full to APB connects which has the accompanying highlights:

- 32-bit AXI slave and APB ace interfaces.

- PCLK clock area totally free of ACLK clock space.

- Support up to 16 APB peripherals

- Burst length is 32 bits

- Support the PREADY flag which means hold up states on AXI.

- An mistake on any move brings about SLVERR as the AXI read/compose reaction.

#### 8.1 Future extension

At the point when perused ask for and compose ask for are at the same time happens the scaffold gives the high need to peruse ask. This condition makes the race condition in APB connect.

For instance FIFO has just a single date thing to peruse operation. On the off chance that read and compose demands are all the while happens the scaffold initially execute the read demand and it read the single date thing from the fifo and now the read date fifo was unfilled.

Again read and compose demands are at the same time happens again it execute read ask for however there is no information thing in read information fifo so exchange will come up short. This circumstance is called race condition.

So on the off chance that you can stay away from this condition it will be more productive. Also, another possibility is expanding the blasted length.

# 8.2 Applications

- Computing: Net book, Smart book, Tablet, eReader, Thin customer.

- Mobile Handset: Smartphone's, Feature telephones.

- Automotive: Infotainment, Navigation.

- Digital Home: Set-top Box, Digital TV, Blu-Ray player, Gaming comforts

# 9 References

- 1. Outline and Implementation of APB Bridge in view of AMBA 4.0 (IEEE 2011), ARM Limited.

- 2. http://en.wikipedia.org/wiki/System\_on\_a\_chip#Structure

- $3.\ Power.org\ Embedded\ Bus\ Architecture\ Report\ Presented\ by\ the\ Bus\ Architecture\ TSC\ Version\ 1.0-11\ April\ 2008$

- 4. http://www.arm.com/items/framework ip/amba/amba-open-specifications.php

- 5. ARM, "AMBA Protocol Specification 4.0", www.arm.com, 2010.ARM, AMBA Specification (Rev 2.0).

- 6. AMBA® 4 AXI4™, AXI4-Lite™, and AXI4-Stream™ Protocol Assertions Revision: r0p0 User Guide.

- 7. AMBA® APB Protocol Version: 2.0 Specifications.

- 8. ASB Example AMBA System Technical Reference Manual Copyright © 1998-

# 10.Short biography

**M.Poojitha** is pursuing M.Tech from Dept of ECE, DVR College Of Engineering and Technology, Kashipur, Sangareddy, Medak, Telangana, India. She is currently working on project work titled "UTILIZATION OF APB INTERFACE IN LIGHT OF AMBA 4.0". Under the guidance of **Tejender Singh**

Mr. **Tejender Singh** is a Post graduate in ECE. He is a Assistant Professor of ECE, DVR College Of Engineering and Technology, Kashipur, Sangareddy, Medak, Telangana, India.. He has 7 Years of UG & PG Level Teaching Experience. Ratified as Assistant Professor by the JNTU- Hydarabad

Mrs.**P.Prasanna Kumari** is a Post graduate in ECE. She is a HOD of ECE, DVR College Of Engineering and Technology, Kashipur, Sangareddy, Medak, Telangana, India. She has 16 Years of UG & PG Level Teaching Experience. Ratified as Associate Professor by the JNTU- Hydarabad