# International Journal of Advance Engineering and Research Development

Volume 4, Issue 6, June -2017

## Performance Evaluation of SRAM CELL Sense Amplifiers

**L Rangaiah<sup>1</sup>**

Ph.D Scholar, Rayalaseemauniversity

Kurnool

**K. Srinivasa Rao<sup>2</sup>**

TRR College of Engineering

Hyderabad

**Rajendraprasad S<sup>3</sup>**

VNR VJET, Hyderabad

### INTRODUCTION

SRAMs are used as cache memory; hence it must perform both read & write operations at high speed along with low power consumption. But its peripheral circuits can adversely affect the overall speed and power of the system. Among all the peripherals of a SRAM memory, sense amplifier plays a major role. It is used to sense or read the data stored or written onto the selected memory bit. The performance of sense amplifiers strongly affects both memory access time and overall power consumption. Sense amplifier is thus used to convert this small voltage swing to a full logic signal [1-4]. To improve the speed and overall performance of memory it is necessary to understand and analyze different types of sense amplifiers. According to the demand of situation appropriate sense amplifier must be used as every design has its own advantage and disadvantage. The main aim of the paper is to design the SRAM cell with different sense amplifiers using HSPICE and calculate various performance characteristics and compare them.

**Keywords:** SRAM, Sense Amplifier, CSA, VSA, CTSA, Power, Delay

### 1. SENSE AMPLIFIERS

In modern computer memory, a sense amplifier is one of the elements which make up the circuitry on a semiconductor memory chip (integrated circuit); the term itself dates back to the era of magnetic core memory. A sense amplifier is part of the read circuitry that is used when data is read from the memory; its role is to sense the low power signals from a bit-line that represents a data bit (1 or 0) stored in a memory cell, and amplify the small voltage swing to recognizable logic levels so the data can be interpreted properly by logic outside the memory [5-8]. Modern sense-amplifier circuits consist of two to six (usually four) transistors, while early sense amplifiers for core memory sometimes contained as many as 13 transistors. There is one sense amplifier for each column of memory cells, so there are usually hundreds or thousands of identical sense amplifiers on a modern memory chip. As such, sense amplifiers are one of the only analog circuits in a computer's memory subsystem. The design objectives of sense amplifier includes Minimum sense delay, Required amplification, Minimum power consumption, Restricted layout and High reliability and Tolerance.

There are different types of sense amplifiers that can be used in SRAM, but in this paper the following three sense amplifiers are designed:

- i) Cross Coupled Voltage Sense Amplifier

- ii) Current Sense Amplifier

- iii) Charge Transfer Sense Amplifier

The simplest Voltage Sense Amplifier is the differential couple. When a cell is being read, a small voltage swing appears on the bit line which is further amplified by differential couple and use to drive digital logic. However the bit line voltage swing is becoming smaller and is reaching the same magnitude as bit line noise, the voltage sense amplifier become unusable.

The fundamental reason for applying current mode sense amplifier in sense circuit is their small input impedances. Benefits of small input and output impedances are reductions in sense circuit delays, voltage swings, cross talking, substrate currents and substrate voltage modulations. The operation of the CTSA is based on the charge re distribution mechanism between very high bit line capacitance and low output capacitance of the sense amplifier. A differential charge transfer amplifier takes advantage of the increased bit-line capacitance and also offers a low-power operation without sacrificing the speed [9-12].

#### 1.1. CROSS COUPLED VOLTAGE SENSE AMPLIFIER (VSA)

Sense amplifier which detects the voltage difference on the bit lines is called voltage mode sense amplifier. There are some voltage mode sense amplifiers like single ended sense amplifiers, differential amplifiers and Cross coupled sense amplifiers. Different types of sense amplifier are used in different types of memory cells according to the proper design and efficient performance.

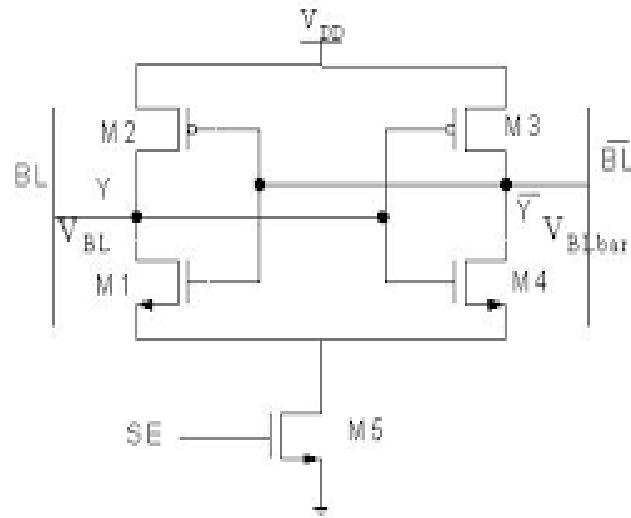

In the circuit shown IN Fig. 1, M1- M4 forms cross-coupled inverters whereas M5 is the driver transistor. There is voltage on BL and BLB which are charged and discharged when the read operation is initiated and are connected to this sense amplifier. Due to positive feedback, higher voltage level goes to VDD and other level goes towards zero. In the basic cross-coupled SA, the nodes BL and BLB are input and output terminals at the same time.

Let us suppose that the bit stored in the memory cell is logic '1' i.e., Q=1 so thus bit stored in QB=0. Due to this, voltage on BL remains constant but voltage on BLB discharges to certain extent. This BL voltage is charged to

VDD and the BLB voltage goes to zero. With this, due to the voltage VDD on BL, it is determined the bit stored in cell is '1'.

The following fig. 1 shows the circuit of cross coupled voltage sense amplifier.

Fig. 1: Cross Coupled Voltage Sense Amplifier

The W and L values of the transistors used in the memory cell are given by:

Width of NMOS is  $0.245\mu\text{m}$  and its length is  $0.18\mu\text{m}$  making the w/l ratio equal to 1.36. Width of PMOS is  $0.2\mu\text{m}$  and its length is  $0.18\mu\text{m}$  making the w/l ratio equal to 1.11. Width of Access transistors NMOS is  $0.3\mu\text{m}$  and its length is  $0.2\mu\text{m}$  making the w/l ratio equal to 1.5. The transistors used in sense amplifier have the following respective w and l values. NMOS transistors (M1 and M4) has a width of  $0.6\mu\text{m}$  and length of  $0.18\mu\text{m}$  making the w/l ratio equal to 3.3. PMOS transistors (M2, M3 and M5) has a width of  $2.5\mu\text{m}$  and length of  $0.18\mu\text{m}$  making the w/l ratio equal to 13.8.

## 1.2. CURRENT SENSE AMPLIFIER (CSA)

In advanced memories the capacitances of the bit line is increasing due to technology scaling and the increasing number of cells attached to the column. In such memories voltage mode cannot keep up to their performance thereby leading to the need for faster sensing techniques that are not affected by the bit line capacitance. Current sensing is typically 17-20% faster than voltage sensing. Current Sense Amplifier can be enabled faster than voltage mode, as current sensing does not depend on differential discharging of large bit-line capacitance. The bit-line swing for current sensing is 35-40% less than the voltage mode, but the energy saved with reduced bit-line swing is compensated by the static power dissipation of the current sense amplifier.

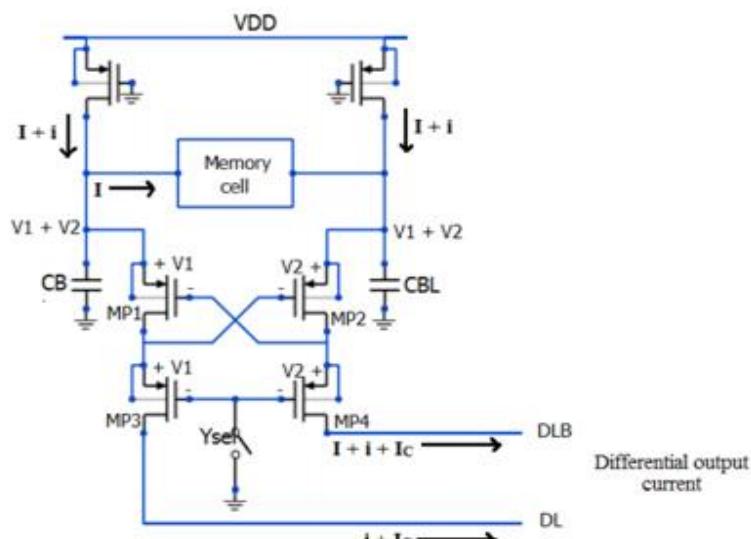

Current mode sense amplifiers (shown in fig.2) are applied to reduce the sense circuit delays as they provide low common input/output impedances. The small input impedance presented to the bit-lines result in reduced voltage swings, cross-talk and substrate currents.

Fig. 2: Current Sense Amplifier

Current mode sense amplifier is used to detect the current difference between the bit lines to determine whether a '1' or '0' is stored in the memory cell. It directly measures the cell read current and transfers to the output circuits. This approach can overcome the restriction of gain reduction brought on by voltage mode sense amplifier at low power supply voltage. The simplest structure of the current mode sense amplifier is described in Fig. 2.

The Conventional Current Sense Amplifier basically consists of four equal sized PMOS transistors as shown in Fig.2. It features a current sensing character since it represents a virtual short circuit to the bit lines, which transfer the cell current directly to the output circuits. If memory cell stores '0' then when it is accessed, it draws some current. The difference in the current flowing through both branches will be equal to cell current. The current in DLB is higher than current in DL as shown in Fig.2. This differential current is used to find whether the stored bit in the SRAM cell is either 0 or 1.

The W and L values of the transistors used in the memory cell are given by:

Width of NMOS is  $1\mu\text{m}$  and its length is  $50\text{nm}$  making the w/l ratio equal to 20. Width of PMOS is  $1.5\mu\text{m}$  and its length is  $50\text{nm}$  making the w/l ratio equal to 30. Width of Access transistors NMOS is  $1.5\mu\text{m}$  and its length is  $50\mu\text{m}$  making the w/l ratio equal to 30. The transistors used in this sense amplifier are all PMOS transistors (MP1, MP2, MP3 and MP4) and have the following respective w and l values. PMOS transistor has a width of  $0.1\mu\text{m}$  and length of  $50\mu\text{m}$  making the w/l ratio equal to 2.

### 1.3. CHARGE TRANSFER SENSE AMPLIFIER (CTSA)

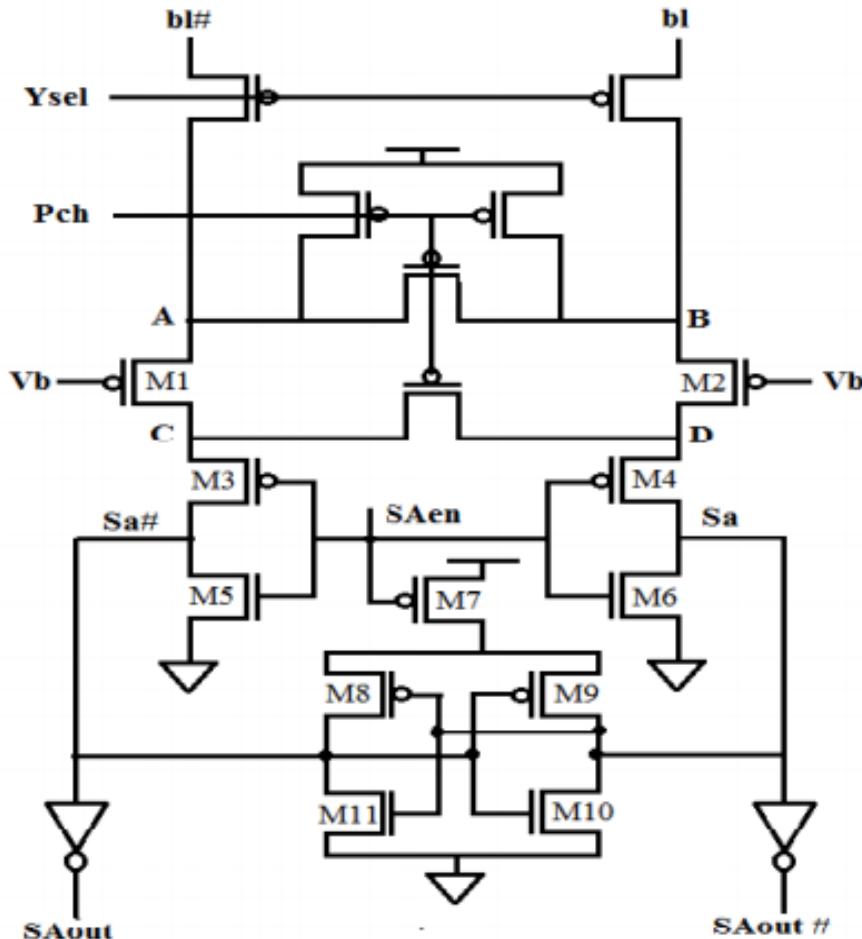

The Charge Transfer Sense Amplifier (CTSA) operates by making use of the charge redistribution from high capacitance bit-lines to the low capacitance sense amplifier output nodes. This results in high speed operation and lower power consumption due to low voltage swing on the bit-lines. The circuit diagram of a CTSA is shown in Fig. 3. The basic concept behind charge-transfer amplification is to produce voltage gain by exploiting charge conservation among capacitive devices. For a series connection of two capacitive elements in a system for which charge is conserved, the product of the voltage across the first element and its capacitance must be equal the product of the voltage across the second element and its capacitance as shown in the following equation.

$$C_{\text{small}} * V_{\text{small}} = Q = C_{\text{large}} * V_{\text{large}}$$

The basic operation of CTSA is based on the charge redistribution from high bit-line capacitance to the low capacitance of the nodes  $S_a$  and  $S_{a\#}$ . This charge redistribution results in high-speed operation and low bit line swing.

The circuit consists of two parts. First is the common gate cascade formed by M1, M3 and M5 (and M2, M4 and M6), with PMOS M1 and M2 biased at  $V_b$ . Second, the cross-coupled inverters formed by M7 through M11 latches the output of the common-gate amplifier ( $S_a$  and  $S_{a\#}$ ). In the pre-charge phase, the bit-lines and all the intermediate nodes (A, B, C and D) are pre-charged high. The output of the common-gate amplifier ( $S_a$  and  $S_{a\#}$ ) is pre-discharged low by keeping  $S_{Aen}$  high. In the evaluation phase,  $P_{ch}$  is pulled high and  $Y_{sel}$  is grounded to select a column. CTSA is enabled by pulling  $S_{Aen}$  low. Suppose, the bit-line  $bl\#$  is going low. As the voltage of the  $bl\#$  goes near  $V_b + |V_{thp}|$ , M1 goes into sub-threshold region of operation preventing the output node  $S_{a\#}$  from getting charged. However, the other bit-line  $bl$  remains high and charges the output node  $S_a$  to high. Initially, NMOS pair M10 and M11 helps in rejecting the common-mode noise and thereafter helps in latching the value sensed by the common gate amplifier.

The bias voltage  $V_b$  is set at  $0.3\text{V}$ . It is critical to set this voltage at the right value as the charge transfer device M1/M2 cuts off when its input source voltage falls to  $V_b + V_{tp}$ . Setting  $V_b$  at a higher value causes the charge transfer device to be cut off early and not have the differential voltage propagate to the sense nodes  $S_a$  and  $S_{a\#}$ . Setting this voltage too low prevents the charge transfer device from entering the sub-threshold region and causes the cross coupled positive feedback inverter to further discharge the bit-line resulting in higher pre-charge power.

Fig.3: Charge Transfer Sense Amplifier

The W and L values of the transistors used in the memory cell are given by:

Width of NMOS is  $1.5\mu\text{m}$  meters and its length is  $50\text{nm}$  making the w/l ratio equal to 30. Width of PMOS is  $1\mu\text{m}$  and its length is  $50\text{nm}$  making the w/l ratio equal to 20. Width of Access transistors NMOS is  $1\mu\text{m}$  and its length is  $50\text{nm}$  making the w/l ratio equal to 20. The pre-charging transistors of this sense amplifier are all PMOS transistors (M1 and M2) having width of  $0.25\mu\text{m}$  and length of  $50\text{nm}$  making the w/l ratio equal to 5. The remaining transistors have the following values of NMOS transistors (M5, M6, M10 and M11) have a width of  $0.25\mu\text{m}$  and length of  $50\mu\text{m}$  making w/l ratio equal to 5. PMOS transistors (M3, M4, M7, M8 and M9) have a width of  $4\mu\text{m}$  and length of  $50\text{nm}$  making w/l ratio equal to 80.

## 2. RESULTS

The various sense amplifier circuits are implemented in HSPICE (H Simulation Program for Integrated Circuit Emphasis) and their performance is evaluated by calculating various parameters like read delay, average power and area of the circuit (in terms of number of transistors) in the 45nm technology with the power supply  $V_{DD} = 3\text{V}$ .

### 2.1. CROSS COUPLED VOLTAGE SENSE AMPLIFIER (VSA)

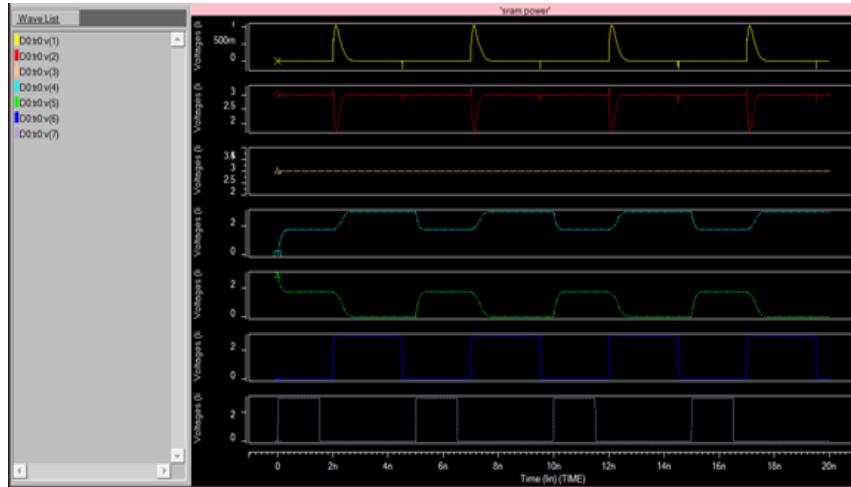

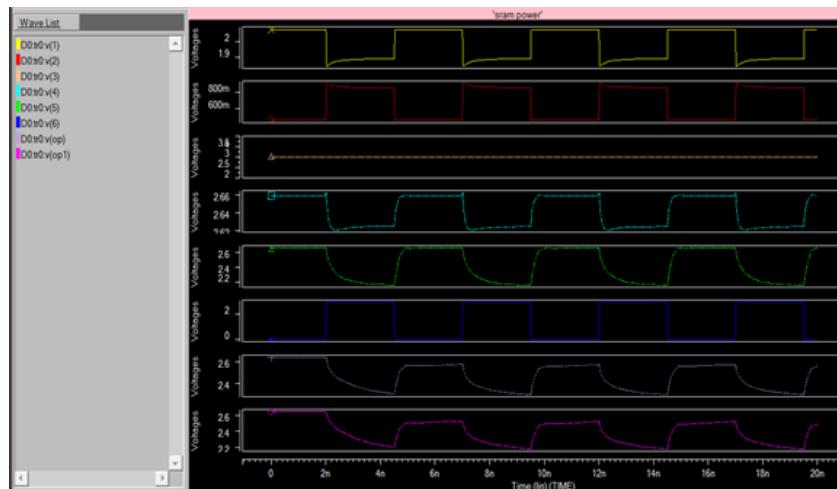

The waveforms of Cross Coupled Voltage Sense Amplifier are shown below in the fig. 4. The nodal voltages are described as  $V(1) = V(q_1)$  where  $q_1$  is the complement of the bit stored in the cell,  $V(2) = V(q)$  where  $q$  is the bit stored in the cell,  $V(3) = V_{DD}$ , power supply of the circuit,  $V(4) = V(bl)$  and  $V(5) = V(bl_1)$  where  $bl$  is the bit-line associated to  $q$  and  $bl_1$  is the bit-line associated to  $q_1$ . These bit-line are used as reference lines for read and write operations taking in SRAM cell. Finally, for selection of this particular memory cell word line has to be high and it is given by  $V(6) = V(wl)$  and  $V(7) = V(pc)$ , here,  $pc$  stands for pre-charging of bit lines which is mandatory for read operation.

Initially, pre-charging is on and word-line is off i.e., pre-charging signal is high and word-line signal is low and the bit stored in cell is given by  $q$  which is shown in figure as  $3\text{V}$  and thus,  $q_1$  reads  $0\text{V}$  as it is the complement of  $q$ . During this phase, both  $bl$  and  $bl_1$  are pre-charged to certain value and then when word-line goes high, the cell is selected and based on the values stored in their respective  $q$  and  $q_1$ , the corresponding  $bl$  and  $bl_1$  charge and discharge. As the value stored in the bit is logic 1,  $q=3\text{V}$  and  $q_1=0\text{V}$  so,  $bl_1$  is discharging and  $bl$  is charging. Eventually, at the end of cycle,  $bl$  reaches  $3\text{V}$  and  $bl_1$  becomes  $0\text{V}$  thus helping us in determining the stored bit in the cell.

Fig.4: Simulated waveforms of Cross Coupled Voltage Sense Amplifier

## 2.2. CURRENT SENSE AMPLIFIER (CSA)

The waveforms of Current Sense Amplifier are shown below in the fig. 5. The nodal voltages are described as  $V(1) = V(q)$  where  $q$  is the bit stored in the cell,  $V(2)=V(q1)$  where  $q1$  is the complement of the bit stored in the cell,  $V(3)=V_{DD}$ , power supply of the circuit,  $V(4)= V(bl)$  and  $V(5)=V(bl1)$  where  $bl$  is the bit-line associated to  $q$  and  $bl1$  is the bit-line associated to  $q1$ . These bit-line are used as reference lines for read and write operations taking in SRAM cell.  $V(op)$  and  $V(op1)$  denote the output lines. Finally, for selection of this particular memory cell word line has to be high and it is given by  $V(6)=V(wl)$ .

Initially, pre-charging is on and word-line is off i.e., pre-charging signal is high and word-line signal is low and the bit stored in cell is given by  $q$  which is shown in figure as 3V and thus,  $q1$  reads 0V as it is the complement of  $q$ . During this phase, both  $bl$  and  $bl1$  are pre-charged to certain value and then when word-line goes high, the cell is selected and based on the values stored in their respective  $q$   $q1$ , the corresponding  $bl$  and  $bl1$  charge and discharge. As the value stored in the bit is logic 1,  $q=3V$  and  $q1=0V$  so,  $bl1$  is discharging and  $bl$  is charging.

Fig. 5: Simulated waveforms of CSA

The  $op$  and  $op1$  are the results obtained where it is clear that  $op$  decreases to a value around 2.3V whereas  $op1$  decreases to a value 2.2V. This small difference on  $op$  and  $op1$  lines is considered and the bit stored in the cell is read out. As the difference between  $op$  and  $op1$  is positive, the bit stored in the memory cell is logic 1. If the difference between  $op$  and  $op1$  is negative, then it is evident that the bit stored in memory cell is logic 0.

## 2.3. CHARGE TRANSFER SENSE AMPLIFIER (CTSA)

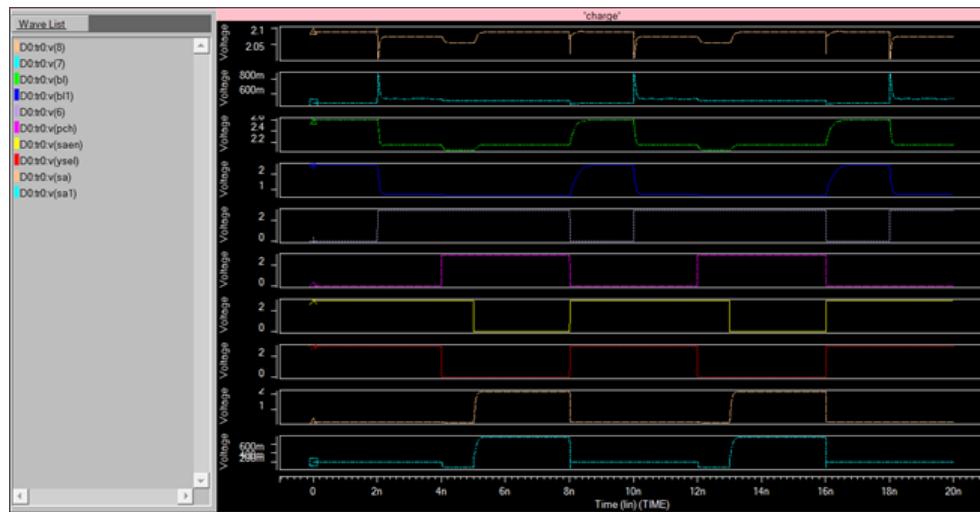

The waveforms of Charge Transfer Sense Amplifier are shown below in the fig. 6. The nodal voltages are described as  $V(8) = V(q)$  where  $q$  is the bit stored in the cell,  $V(7)=V(q1)$  where  $q1$  is the complement of the bit stored in the cell,  $V(3)=V_{DD}$ , power supply of the circuit,  $V(bl)$  and  $V(bl1)$  represent bit-line voltages,  $V(saen)$  is the sense amplifier enable signal which turns on the amplifier after the discharging and charging of bit-lines,  $V(ysel)$  and  $V(pch)$  are for the pre-charging of sense amplifier. Finally  $V(sa)$  and  $V(sa1)$  are the outputs of the sense amplifier.

After the charging and discharging of bit-lines  $b_1$  and  $b_{11}$ , in the pre-charge phase, the bit-lines and all the intermediate nodes ( $A, B, C$  and  $D$ ) are pre-charged high. The output of the common-gate amplifier ( $S_a$  and  $S_{a1}$ ) is pre-discharged low by keeping  $saen$  high. In the evaluation phase,  $pch$  is pulled high and  $ysel$  is grounded to select a column. CTSA is enabled by pulling  $saen$  low. Here,  $b_{11}$  is discharging faster and to a smaller value and thus  $sa1$  is low and  $sa$  is high. The bit stored in the cell is given by  $sa$ .

Fig. 6: Simulated waveforms of CTSA

#### 2.4. COMPARISON OF THREE SENSE AMPLIFIERS

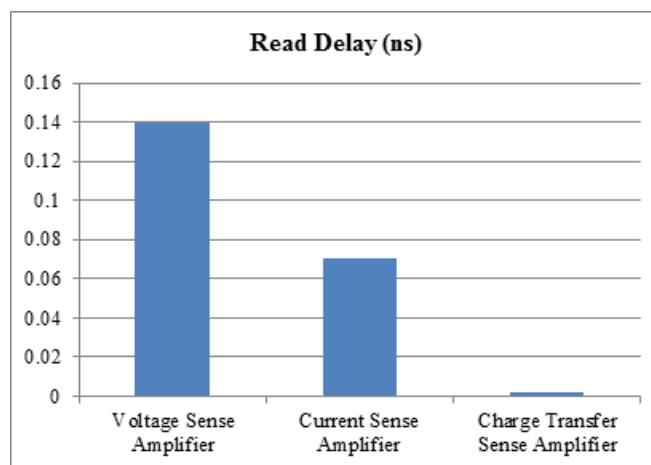

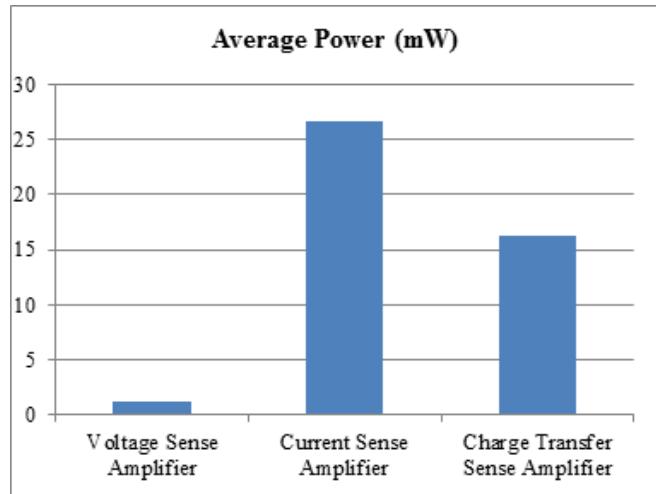

The Table 1 shows the comparison of different parameters among the three sense amplifiers.

Table 1: Comparison of three sense amplifiers

| Parameter | Average Power (mW) | Read Delay (ns) | No. of Transistors |

|-----------|--------------------|-----------------|--------------------|

| VSA       | 1.19               | 0.14            | 5                  |

| CSA       | 26.7               | 0.07            | 6                  |

| CTSA      | 16.3               | 0.0019          | 17                 |

The following Fig. 7 shows the representation of comparison of delay parameter between the three different circuits of sense amplifier. It shows that voltage sense amplifier has more delay (0.14 ns) compared to the current sense amplifier which has 0.07ns delay. Among the three circuits, charge transfer sense amplifier has very less delay of 1.9ps.

Fig. 7: Comparison of read delays of different sense amplifiers

The Fig. 8 shows the representation of comparison of average power parameter between the three different circuits of sense amplifier. It shows that voltage sense amplifier has less average power (1.19mW) compared to the current sense amplifier which has 26.7 mW and also charge transfer sense amplifier which has 16.3mW

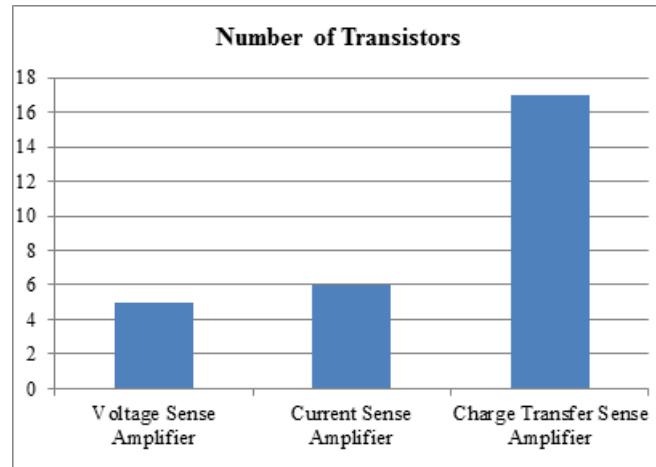

The Fig. 9 shows the representation of comparison of number of transistors in different sense amplifier circuits. It shows that voltage sense amplifier has less number of transistors (5) thereby has less area than current sense amplifier

which has 6 transistors. Among the three circuits, charge transfer sense amplifier has more area since it has more number of transistors (17).

Fig. 8: Comparison of average power of different sense amplifiers

Fig.9: Comparison of number of transistors in different sense amplifiers

### 3. CONCLUSION

This paper presented the performance evaluation of three different sense amplifier topologies – Voltage Sense Amplifier (VSA), Current Sense Amplifier (CSA) and Charge Transfer Sense Amplifier (CTSA) by implementing them using HSPICE in 45nm technology with a supply  $V_{DD}$  of 3V. The comparison of different parameters between these three circuits is shown in the Table 1. It shows that among the three topologies, CSA is the best choice with minimum delay. CSA is faster than VSA with reduction in delay. But it consumes more power dissipation than VSA and CTSA. CTSA shows reduction in delay compared to VSA. Now, power obtained in VSA is 1.19mW which is less than CSA having 26.7mW whereas the read time delay in voltage sense amplifier is 0.14ns which is greater than 0.07ns of CSA. Thus, using CTSA, read time delay problem overcame by having done read operation in only 1.93 ps.

### REFERENCES

- [1] Parita Patel, Sameena Zafar and Hemant Soni, “Performance of Various Sense Amplifier Topologies in sub100nm Planar MOSFET Technology”, Volume 3, Issue 2, March – April 2014.

- [2] Rajendra Prasad S, B K Madhavi and K Lal Kishore, “Reduction of Leakage-Power in CNTFET SRAM Cell using Stacked Sleep Technique at 32nm Technology,” IEEE International Conference on Advances in Engineering, Science and Management (ICAESM-2012), Nagapattinam, India, March 30-31, 2012, pp.244-248.

- [3] Igor Arsovski, “High-Speed Low-Power Sense Amplifier Design”, November 12, 2001.

- [4] Dr. Rajendra Prasad S, Dr. B K Madhavi and Dr. K Lal Kishore, “Low-Leakage CNTFET SRAM Cells,” Elsevier Third International Conference on Recent Trends in Computing (ICRT 2015), Delhi, India, Published in Elsevier Journal Procedia Computer Science, volume.57, pages.1049-1056, March 12th – 13th, 2015.

- [5] Meenu Rani Garg, Anu Tonk, "A Study of Different Types of Voltage & Current Sense Amplifiers used in SRAM", Vol. 4, Issue 5, May 2015.

- [6] Rajendra Prasad S, B K Madhavi and K Lal Kishore, "Design of 32nm Forced Stack CNTFET SRAM Cell for Leakage Power Reduction," IEEE International Conference on Computing, Electronics and Electrical Technologies (ICCEET-2012), Nagercoil, India, March 21-22, 2012, pp. 629-633.

- [7] Jyoti hooda, Sarita ola, Manisha saini," Design and Analysis of a low Power CMOS Sense Amplifier for Memory Application", Volume-2, Issue-5, April 2013

- [8] B. Witch, "Current Sense Amplifiers for Embedded SRAM in High-Performance System-on-a-chip-designs", edition 2003.

- [9] Abhishek Agal, Pardeep, Bal Krishan, "6T SRAM Cell: Design And Analysis", Vol. 4, Issue 3, Version 1, March 2014, pp.574-577.

- [10] Debasis Mukherjee, Hemanta Kr. Mondal and B.V.R. Reddy," Static Noise Margin Analysis of SRAM Cell for High Speed Application", Vol. 7, Issue 5, September 2010.

- [11] Rajendra Prasad S, B K Madhavi and K Lal Kishore, "Design of a 32nm 7T SRAM Cell based on CNTFET for Low Power Operation," IEEE International Conference on Devices Circuits and Systems (ICDCS-2012), March 15-16, 2012, pp.443-446.

- [12] Rajendra Prasad S, B K Madhavi and K Lal Kishore, "Low Leakage-Power SRAM cell design using CNTFETs at 32nm Technology," Springer 3rd International Conference on Communication, Network, and Computing (CNC-2012), Chennai, India, February 24-25, 2012, pp. 165-171.